Doodling Shake Bot DIY STEM Kit

$8.99$4.95

Posted on: Jun 26, 2005

A new technique for fabricating liquid cooling channels onto the backs of high-performance integrated circuits could allow denser packaging of chips while providing better temperature control and improved reliability.

Developed at the Georgia Institute of Technology, the wafer-level fabrication technique includes polymer pipes that will allow electronic and cooling interconnections to be made simultaneously using automated manufacturing processes. The low-temperature technique, which is compatible with conventional microelectronics manufacturing processing, allows fabrication of the microfluidic cooling channels without damage to integrated circuits.

The on-chip microfluidic technique was described June 7th at the eighth annual IEEE International Interconnect Conference in San Francisco, CA. A paper further describing the technology and interconnect system will be published in the proceedings of ASME InterPACK, to be held July 17-22 in San Francisco, CA. The research was sponsored by the Microelectronics Advanced Research Corporation (MARCO) and the Defense Advanced Research Projects Agency (DARPA).

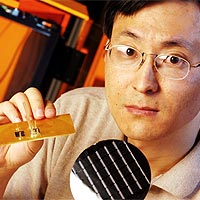

“This scheme offers a simple and compact solution to transfer cooling liquid directly into a gigascale integrated (GSI) chip, and is fully compatible with conventional flip-chip packaging,” said Bing Dang, a Graduate Research Assistant in Georgia Tech’s School of Electrical and Computer Engineering. “By integrating the cooling microchannels directly into the chip, we can eliminate a lot of the thermal interface issues that are of great concern.”

As the power density of high-performance integrated circuits increases, cooling the devices has become a more significant concern. Conventional cooling techniques, which depend on heat sinks on the backs of ICs to transfer heat into streams of forced air, will be unable to meet the needs of future power-hungry devices – especially 3D multi-chip modules that will pack more processing power into less space.

High temperatures can cause early failure of the devices due to electromigration. By controlling average operating temperature and cooling hot-spots, liquid cooling can enhance reliability of the integrated circuits, Dang noted. Lower operating temperatures also mean a smaller thermal-excursion between silicon and low-cost organic package substrates that expand at different rates.

Some liquid cooling techniques are already in production or at a research stage, circulating liquid through separate cooling modules attached to the integrated circuits, or through microchannels fabricated onto the back of chips using high-temperature bonding techniques. These approaches have disadvantages, including limited heat transfer through the modules and potential thermal damage to the chips caused by bonding temperatures that range from 400 to 700 degrees Celsius.

The Georgia Tech approach allows a simple monolithic fabrication of cooling channels directly onto integrated circuits using a CMOS-compatible technique at temperatures of less than 260 degrees Celsius.

“Once the integrated circuit is fabricated, it cannot withstand high temperatures without causing damage,” said Dang. “People are looking at liquid cooling in all forms to solve the thermal issues affecting advanced integrated circuits, and the goal is to prevent damage to the chips. We have invented a new way to do it.”

The Georgia Tech researchers, who include Paul Joseph, Muhannad Bakir, Todd Spencer, Paul Kohl and James Meindl, begin by etching trenches more than 100 microns deep on the back of the silicon wafer.

They then spin-coat a layer of high-viscosity sacrificial polymer onto the back of the chip, filling in the trenches. Next, a simple polishing step removes excess polymer.

The filled trenches are then covered by a porous overcoat, and the chip is gradually heated in a nitrogen environment. The heating causes the sacrificial polymer filling the trenches to decompose and leave the channels through the porous overcoat, leaving microfluidic channels behind. The porous overcoat is then covered with another polymer layer to make a watertight system.

In addition to the cooling channels, the researchers have also built through-chip holes and polymer pipes that would allow the on-chip cooling system to be connected to embedded fluidic channels built into a printed wiring board. They have already demonstrated that the on-chip microfluidic channels can be connected at the same time the IC is connected electronically – using a conventional automated process known as flip-chip bonding.

The system would use buffered de-ionized water as its coolant. Self-contained cooling systems would circulate coolant using a centimeter-size micro-pump, while more complex equipment could use a centralized circulation system. The researchers have so far demonstrated that their microchannels can withstand pressure of more than 35 pounds per square inch – the equivalent to the air pressure used in passenger-car tires.

Calculations show that the system, which can have either straight-line or serpentine microchannel configurations, should be able to cool 100 watts per square centimeter. Heat removal capacity depends on the flow rate of the coolant and its pressure, with smaller diameter microchannels more efficient at heat transfer.

Dang expects the technology to be used first in high-performance specialty processors that can justify the cost of the cooling system. So far, the researchers have demonstrated continuous liquid flow on a chip for several hours without failure, but additional testing is still needed to confirm long-term reliability, he added.

By eliminating the large heat sinks and heat spreaders, along with high-aspect ratio fins, the technology could allow denser packaging of integrated circuits, making 3D packaging feasible.

“The challenge of 3D integration now is that if you have several chips stacked on one another, there is no way to cool the chips in between,” Dang said. “If we have microchannels on the back side of each chip, we could pump liquid through them and cool all of the chips.”

'There are two ways to live your life. One is as though nothing is a miracle. The other is as though everything is a miracle.'

'There are two ways to live your life. One is as though nothing is a miracle. The other is as though everything is a miracle.'